概述

PCI-SIG®开发了PCI Express®(PCIe) 6.0以满足新兴应用的高速数据传输需求。随着数据速率翻倍和其他增强的性能指标,PCIe 6.0 增加了高速互连设计的复杂性。工程师需要选择合适的信号完整性测试解决方案来验证其产品是否符合 PCIe 6.0 标准。

本文概述了PCIe 6.0里的新增的技术,例如 PAM4、前向纠错 (FEC) 和链路均衡。同时,本文还提供了如何选择正确的测试系统来验证 PCIe 6.0 设计的指南。

PCIe 6.0即将到来

PCI-SIG 正在快速开发用于高速设备的下一代 PCIe 互连 I/O 技术,包括硬盘驱动器、固态驱动器 (SSD)、显卡、Wi-Fi 路由器和内部以太网连接。PCIe 6.0 的规范已于 2022 年完成。随着规范的确定,意味着信号完整性工程师已着手开始将 PCIe 6.0 集成到他们的设计计划中。

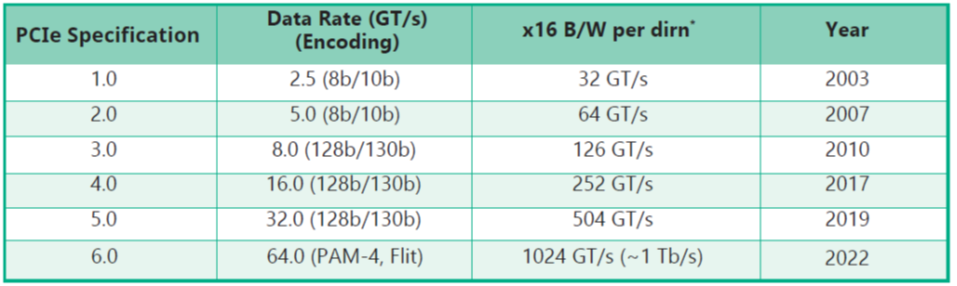

表 1:各代 PCIe 数据速率

表 1 显示了每一代的数据速率。当从 PCIe 5.0 的 32 GT/s 跃升至 PCIe 6.0 的 64 GT/s 时,PSI-SIG 标准委员会仅稍微改变了一致性要求。为了解决信号衰减问题,实施了更严格的通道和连接器损耗以及反射参数。接收端和发射端均衡也进行了微小的改进。尚未制定重大创新来解决与更陡峭的上升-下降时间、更窄的单位间隔 (UIs) 以及与数据速率加倍相关的更大插入损耗相关的预期复杂性。

对于信号完整性工程师来说,验证 PCIe 6.0 设计需要能够准确测量性能以确保一致性的高级测试解决方案。虽然许多测试与前几代类似,但 PCIe 6.0 测试的复杂性和所需的准确性要求测试仪器具有不同的性能阈值。

PCIe 6.0 采用 PAM4

PCIe 6.0 的一项变化是 32 Gbaud PAM4 信号。前五代规范均采用 NRZ。PAM4 将允许该规范的通道范围与 PCIe 5.0 规范保持相似。与所有前代 PCIe 一样,PCIe 6.0 完全向后兼容,因此也支持 NRZ。

尽管基频与 32.0 GT/s NRZ 的 PCIe 5.0 规范相同,但 PAM4 模式需要额外的电路和逻辑来跟踪三眼,以及在流量控制单元 (FLIT) 模式下运行所需的逻辑更改。FLIT被选用于PCIe 6.0 架构,因为它允许对固定大小的数据包进行纠错。由于纠错发生在 FLIT 上,因此循环冗余校验 (CRC) 和重试必须在 FLIT 级别完成。一旦链路在 FLIT 模式下运行,任何降低数据速率的速度更改也必须使用相同的 FLIT 模式。

除了 PAM4 之外,PCIe 6.0 规范还包括错误假设,包括通道上以及通道间错误之间的相关性。PCIe 6.0 技术采用独特的方法,通过将相对较低的第一位误码率 (FBER) 与轻量级、低延迟的前向纠错 (FEC) 相结合来进行初始纠正,从而保持低延迟。然后,强大的 CRC 会检测纠正后仍然存在的任何错误。结果是链路级重试,延迟也非常低。

与 FEC 延迟超过 100+ 纳秒的网络标准不同,PCIe 技术是一种加载-存储协议。因此,它必须严格遵守所有规格,特别是在延迟、功耗和高带宽方面。使用 FEC 和 CRC 允许 PCIe 6.0 实现指定的低延迟,并在大多数情况下减少延迟。它还将实现低复杂性和低带宽开销。

满足新兴应用的性能

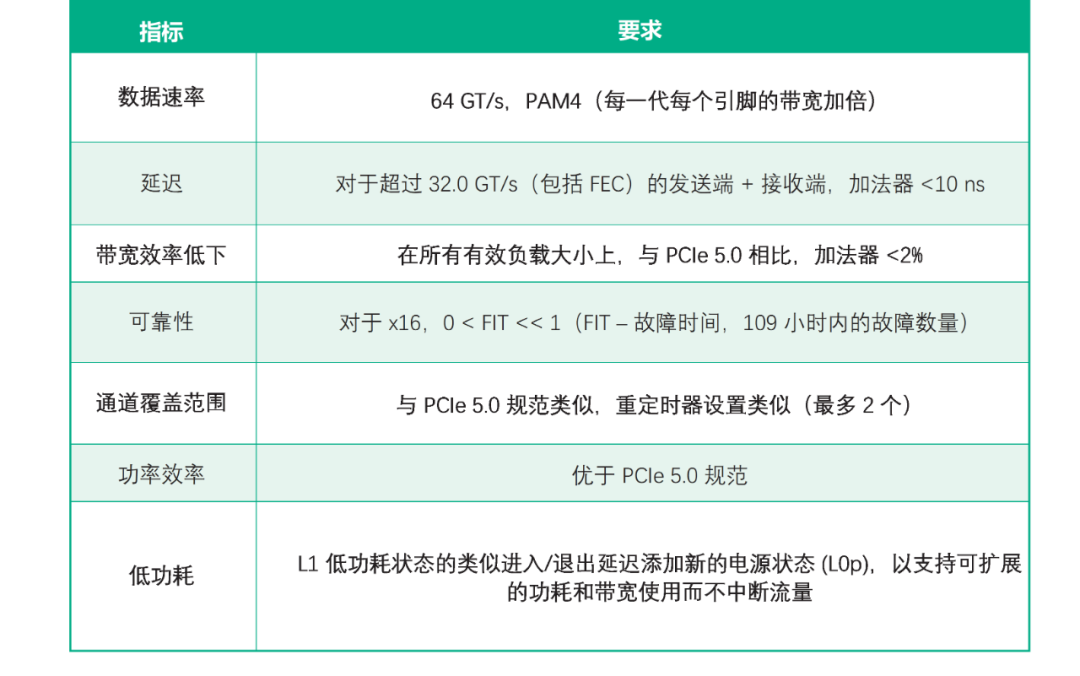

PCI-SIG 正在建立新一代高速互连的性能,以满足物联网、汽车和人工智能等新兴应用的需求。表 2 显示了 PCIe 6.0 的关键指标。PCIe 6.0 规范中使用与 PCIe 5.0 规范相同的基础结构来实现电压和时间裕度方面的通道裕度。

表2:PCIe

表2:PCIe

6.0 的关键指标

PAM4 技术的演进以及 6.0 标准开发下的其他增强规范将影响使用 PCIe 6.0 的 I/O 接口和系统的测试。许多测试(包括BER、链路均衡和 FEC)已经在进行,以验证现有 PCIe 技术的设计。然而,由于新标准的原因,PCIe 6.0 的这些测量参数要复杂得多。

PAM4 对 BER 的影响

PAM4 信号可减少通道损耗,因为它以一半的频率运行,每个 UI 两位。然而,由于 PCIe 6.0 在同一 UI 中有三个眼,因此眼的高度和宽度将会减小。因此,PAM4 的 BER 会高出几个数量级,这就是 FEC 必要的原因。

对于 PCIe 6.0,BER 是 FBER、通道中错误相关性以及通道间错误相关性的组合。FBER 是链路中接收端处发生第一位错误的概率。PSI-SIG 在最终确定 PCIe 6.0 的 10-6 FBER 之前进行了广泛的研究。这是满足

有两种主要机制可以纠正通道内和跨通道的错误。最值得注意的是通过 FEC 和 CRC 错误检测,从而通过链路层重试最终进行纠正。FEC 的工作原理是发送冗余数据,这些数据可用于纠正接收端处的一些错误。CRC 是一种错误检测码,用于验证发送方和接收端之间的数据包传输。

FEC 的重要性

PCI-SIG 为 PCIe 6.0 建立了

FEC 逻辑可以在任何频率下运行。一般来说,期望逻辑将以 1G(或 500 MHz 或 2G)运行,并轻松达到远远小于 2 ns 的延迟。 PCI-SIG 建议使用轻量级 FEC 进行校正。用于检测的非常强大的 CRC 与快速链路级重现相结合,可以处理 FEC 无法纠正的任何错误。只要 FLIT 的重现概率约为 10-6,由于 FEC 延迟或未检测到错误时的重现延迟,就不会有明显的性能影响。 FEC 校正和 CRC 检测相结合可实现重现,有效地纠正几乎所有常见错误。

推荐的方法是建立 FEC 符号错误阈值。通过这样做,工程师可以通过忽略通常在 FEC 环境中纠正的无关紧要的事件,对捕获期间影响模式的错误条件进行更广泛的控制。

为了设置阈值,BERT 会向被测设备 (DUT) 接收输入端生成 PAM4 信号。DUT 确定输入信号的逻辑状态,并循环判定发送输出端中的错误信号以供 BERT 分析。BERT 的内置错误检测器 (ED) 确定 DUT 的决策是否正确。为了获得相关结果,BERT 的抖动和噪声曲线必须符合标准。

在进行测试时,需要注意的是,随机错误并不像突发错误那样有意义。FEC 的校正通常不能超过一定限度。后处理必须超出该限制,以帮助确定 DUT 可能误读传入符号的原因。通过这种方法,工程师能够使用标准 PRBS 模式来测试设备,同时根据 FEC 环境中可能出现问题的事件进行错误检测捕获。

链路均衡

在链路均衡测试中使用受压信号同时评估链路协商和受压接收端容限。接收端和发射端的两项测试必须使用 PCI-SIG 开发的 SigTest 软件进行。

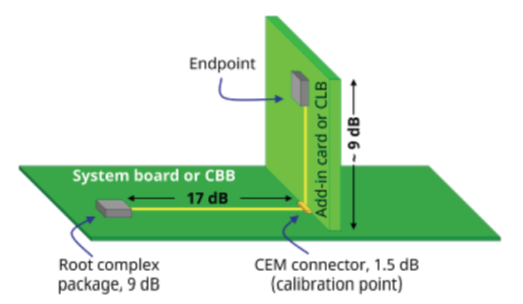

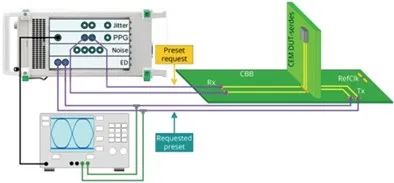

图 1 显示了 CEM 或 BASE 测试示意图。在 CEM 测试中,DUT 由 SerDes 及其安装的附加卡组成。在 BASE 测试中,DUT 由 SerDes 本身组成并安装到系统板上。

图·1:CEM 或 BASE 测试配置图

图·2:安立MP1900A

PPG 应用的信号损伤的屏幕截图

校准发送端加重和抖动设置后,测试过程需要对 SigTest 软件进行多次迭代,以确定正确的测试通道和减值组合。一个“可变 ISI”测试板,具有多种不同走线长度,损耗范围为 34 dB 至 37 dB(以 0.5 dB 为步长)用于应用不同量的损耗和 ISI。DUT 附加卡 (DUT-AIC) 必须能够使用该最大压力信号来协商链路。一旦链路经过协商并且发送端 FFE 和接收端均衡方案经过优化后,DUT 接收端必须以 BER

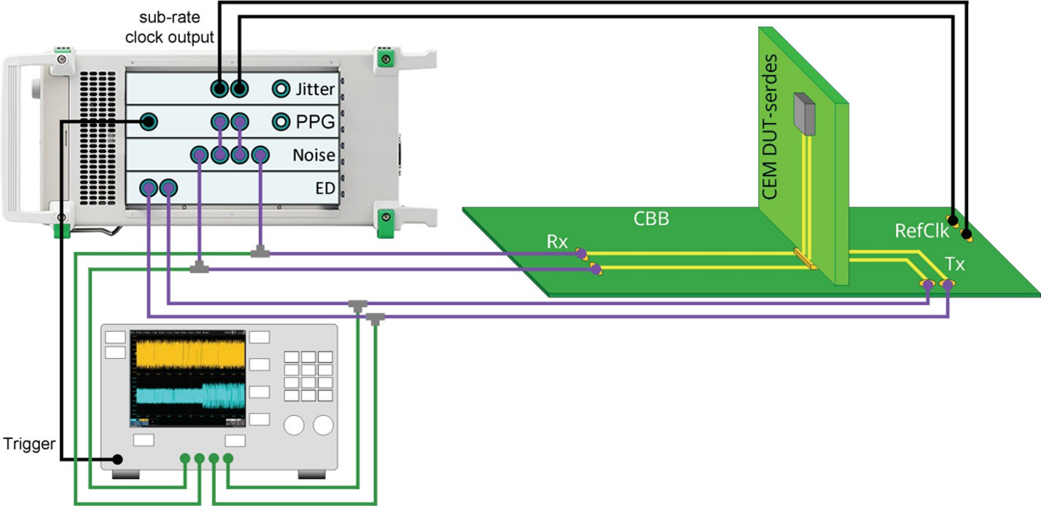

图 3 显示了测试设置。BERT PPG 差分输出被分离,以便信号传输到 DUT 接收端和示波器。DUT 发送输出端也被划分,因此其信号被传输到示波器和 BERT ED(充当参考接收端)。

图3:接收端链路均衡测试配置

测试从 BERT PPG 向 DUT 发送端发送预设请求开始——PHY 层逻辑子块中的协商。DUT 通过更改其 FFE tap 来响应。示波器还接收预设请求。它必须具有一定级别的协议功能来识别预设的测量请求 (tReq)。示波器的触发信号是 tReq 的一个选项,但由于触发电缆的时延,它增加了测量的不确定性。

发送端链路均衡——这是一项必需的一致性测试,用于验证设备是否在链路伙伴请求时在指定时间内正确更改均衡。BERT 请求设备进行均衡更改,同时向示波器发送触发信号,以便可以在电域中测量 DUT 的时延。

BERT PPG 通过 PCIe 物理层逻辑子块协议向 DUT 发送端发送请求(图 4)。BERT PPG 按顺序向 DUT-AIC 发送针对每个 PCIe 数据速率预设的每个 FFE 的请求。DUT 发射端修改其 FFE 方案并传输信号。DUT 发送输出端被分离,以便其信号被发送到示波器和 BERT ED。示波器观察所需的高级均衡变化,而 ED 充当参考接收端,确认预设变化。

BERT 使用 PPG 辅助输出来触发示波器采集每个信号。示波器捕获每个 FFE 预设和每个数据速率的波形。然后,它运行示波器上安装的 SigTest,根据一致性要求评估每个波形。还可以通过 SigTest 创建结果报告。

图4:发射端链路均衡测试配置

JTOL的优点

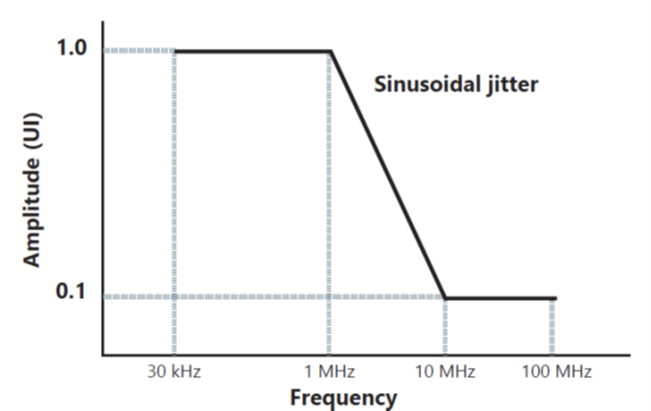

PCIe 6.0 规范并不要求进行抖动容限测试 (JTOL),但它是确定接收端是否可以容忍不同幅度和频率的抖动的绝佳方法。与链路均衡测试类似,使用基于仍符合要求的最坏情况的受压信号。它有ISI、RJ、DMI和CMI。作为一种调试技术或性能裕度分析,JTOL 可以使用任何均衡方案进行测试。然后根据图 5 所示的幅频模板将 SJ 添加到信号中。

图5:确定JTOL 的幅频模板

高幅度抖动应用于低频,低幅度抖动应用于高频。从 1 MHz 到 10 MHz 的滚降遵循指定的 CDR 频率响应。BER 是在模板上测量的。对于所有幅频对,DUT 接收端应遵守BER -6。为了在合理的时间长度内进行测量,通常将BER 测量为BER -3,并外推 BER 概率的斜率以确保BER -6。

选择合适的测试系统

为了准确地进行这些测试,PCIe 6.0 测试系统需要功能丰富、协议感知的误码率测试仪 (BERT) 和示波器。BERT 需要一个内置仪器质量的 PPG(可以应用特定信号损伤的精确级别)和一个内置 ED(能够验证是否符合 PCIe 规范)。BERT 应具有多个以 32 GT/s 运行的 NRZ 码型生成通道和错误检测器,以及以 64 GT/s 运行的 PAM4 通道,以支持 PCIe 6.0 及更早版本。

信号完整性还需要 115 fs 和 12 ps 20% 至 80% 上升/下降时间的低固有抖动。 BERT 需要在超出 PCIe 6.0 规范要求的幅度范围内应用每个所需的信号损伤,如下表所示。

示波器的实时采样带宽应 > 50 GHz。对于发射器信号评估和应力眼接收器容限测试的校准,示波器还必须支持 PCI-SIG 测试软件分析工具。特别是应该具有:

-

自动链路均衡测试

-

眼图和抖动分析

-

自动测试夹具解嵌

-

PCIe PHY 逻辑子块协议解码

结论

PCIe 向 6.0 的演进给信号完整性工程师带来了新的设计挑战。利用由协议感知 BERT 和高速示波器组成的系统进行完善的测试流程,可生成高质量眼图并具有全面的分析工具,这将为新兴应用(尤其是数据中心产品和系统)的复杂高速设计带来更大的信心。